# PD69108/F Datasheet 8-Port PSE PoE Manager

September 2019

# **Contents**

| 1 | Revision  | History                                | . 1 |

|---|-----------|----------------------------------------|-----|

|   | 1.1 Rev   | sion 3.0                               | . 1 |

|   | 1.2 Revi  | sion 2.0                               | . 1 |

|   | 1.3 Revi  | sion 1.7                               | . 1 |

|   | 1.4 Revi  | sion 1.6                               | . 1 |

|   | 1.5 Rev   | sion 1.5                               | . 1 |

|   | 1.6 Revi  | sion 1.4                               | . 1 |

|   | 1.7 Revi  | sion 1.3                               | . 1 |

|   | 1.8 Rev   | sion 1.2                               | . 1 |

|   | 1.9 Revi  | sion 0.6                               | . 1 |

|   | 1.10 Re   | vision 0.5                             | . 2 |

|   | 1.11 Re   | vision 0.4                             | . 2 |

|   | 1.12 Re   | vision 0.3                             | . 2 |

|   | 1.13 Re   | vision 0.2                             | . 2 |

|   | 1.14 Re   | vision 0.1                             | . 2 |

| _ | Dead at 4 |                                        | 2   |

| 2 |           | Overview                               |     |

|   |           | cal Application                        |     |

|   | 2.2 ΤΥΡΙ  | cai Application                        | . 4 |

| 3 |           | al Descriptions                        |     |

|   | _         | c Main Control Module                  |     |

|   | 3.1.1     | Line Detection Generator               |     |

|   | 3.1.2     | Classification Generator               |     |

|   | 3.1.3     | Current Limiter                        |     |

|   | 3.1.4     | Main MOSFET                            |     |

|   | 3.1.5     | Analog-to-Digital Converter (ADC)      |     |

|   | 3.1.6     | Power on Reset (POR)                   |     |

|   | 3.1.7     | Voltage Regulator                      |     |

|   | 3.1.8     | CLK                                    |     |

|   |           | lication Information                   |     |

|   | 3.2.1     | Line Detection                         |     |

|   | 3.2.2     | Legacy (Capacitor) Detection           |     |

|   | 3.2.3     | Classification                         |     |

|   | 3.2.4     | Port Start Up                          |     |

|   | 3.2.5     | Over-Load Detection and Port Shut Down |     |

|   | 3.2.6     | Disconnect Detection                   |     |

|   | 3.2.7     | Over-Temperature Protection            |     |

|   | 3.2.8     | V MAIN Out-of-Range Protection         | 8   |

| 4 | Flectrical Specifications |                                     |    |  |

|---|---------------------------|-------------------------------------|----|--|

|   | 4.1                       | Dynamic Characteristics             | 11 |  |

|   | 4.2                       | Absolute Maximum Ratings            | 13 |  |

|   | 4.3                       | Power Dissipation Information       | 13 |  |

| 5 | Pin I                     | Descriptions                        | 14 |  |

| 6 | Pack                      | kage Specification                  | 18 |  |

|   | 6.1                       | RoHS and Solder Reflow Information  | 18 |  |

|   | 6.2                       | Thermal Specifications              | 20 |  |

|   | 6.3                       | Tape and Reel Packaging Information | 21 |  |

| 7 | Orde                      | ering Information                   | 23 |  |

# 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

#### 1.1 Revision 3.0

Revision 3.0 is published in September 2019. The following is a summary of changes made in revision 3.0 of this document.

- The package marking is updated in the ordering information table. For more information, see

Ordering Information (see page 23).

- Figure 5 is updated.

#### **1.2** Revision **2.0**

Revision 2.0 was published in March 2018. The format of this document was updated to the latest template.

Part marking is updated. For more information, see Ordering Information (see page 23).

#### **1.3** Revision **1.7**

Revision 1.7 was published in July 2015. In revision 1.7 of this document, a NOTE was added specifying "Fuses per port are not required for use in circuits with total power level of up to 3 kW."

#### **1.4** Revision **1.6**

Revision 1.6 was published in June 2013. In revision 1.6 of this document, a full temperature range P/N was added.

#### 1.5 Revision 1.5

Revision 1.5 was published in December 2012. In revision 1.5 of this document, Tape and Reel Data was added.

# 1.6 **Revision 1.4**

Revision 1.4 was published in February 2012. In revision 1.4 of this document, I lim was updated according to UL and IEEE standards.

#### 1.7 **Revision 1.3**

Revision 1.3 was published in January 2012. In revision 1.3 of this document, the Footer address was updated.

#### 1.8 **Revision 1.2**

Revision 1.2 was published in October 2011. In revision 1.2 of this document, Osc was added.

#### 1.9 **Revision 0.6**

Revision 0.6 was published in August 2011. In revision 0.6 of this document, SPI Timing data was added.

# 1.10 Revision 0.5

Revision 0.5 was published in April 2011. In revision 0.5 of this document, minor corrections were made.

#### 1.11 Revision 0.4

Revision 0.4 was published in July 2010. In revision 0.4 of this document, the catalog numbers metrology and Ordering Information was updated.

# 1.12 **Revision 0.3**

Revision 0.3 was published in April 2010. In revision 0.3 of this document, minor corrections were made.

# 1.13 Revision 0.2

Revision 0.2 was published in January 2010. In revision 0.2 of this document, the Power Dissipation was updated.

# 1.14 Revision 0.1

Revision 0.1 was published in November 2009. It was the initial release of this document.

# 2 Product Overview

Microsemi's PD69108/F Power over Ethernet (PoE) manager integrates power, analog, and state-of-the-art logic into a single 48-pin, plastic QFN package. The device is used in Ethernet switches and midspans, enabling network devices to share power and data over the same cable. The PD69108/F device is an eight port, mixed-signal, high-voltage PoE driver.

The PD69108/F enables detection of IEEE802.3at-2009 compliant Type 1 and Type 2 Power Devices (PDs). This ensures safe power feeding and disconnection of ports with full digital control and a minimum of external components.

The PD69108/F device executes all real-time functions as specified in the IEEE802.3af-2003 (AF) and IEEE802.3at-2009 high power (AT) standards. This includes load detection, AF, and AT classification. In addition, the PD69108/F device features Multiple Classification Attempts (MCA) port status monitoring. This provides system-level activities such as power management and MIB support for system management.

The PD69108/F device is designed to detect and disable disconnected ports. This utilizes the DC disconnection methods, as specified in the IEEE 802.3af-2003 and IEEE802.3at-2009 standards.

The PD69108/F device provides PD protection such as over-load, under-load, over-voltage, and short-circuiting. It supports supply voltages ranging from 44 to 57 voltage DC (V<sub>DC</sub>) with no additional power supply sources. The chip includes built-in internal thermal protection. Optionally, the PD69108/F can detect legacy/pre-standard PD devices.

The PD69108/F is a low-power device using an internal MOSFET and an external 0.36  $\Omega$  sense resistor.

# 2.1 Features

- IEEE802.3af-2003 compliant

- IEEE802.3at-2009 compliant, including two-event classification

- Supports pre-standard PD detection

- Supports Cisco devices detection

- Single DC voltage input (44 Vpc to 57 Vpc)

- Input voltage out of range protection

- Wide temperature range: -10 °C to 85 °C

- PD69108F version covering 40 °C to 85 °C

- Over-temperature protection

- Low power dissipation (0.36  $\Omega$  sense resistor and 0.3  $\Omega$  MOSFET RDS(ON)

- Includes reset command pin

- Four times direct address configuration pins

- Continuous port monitoring and system data

- Configurable load current setting

- Configurable AT/AF modes

- Configurable standard and legacy detection mode

- Power soft start mechanism

- On-chip thermal protection

- Voltage monitoring/protection

- Built in 3.3 Vpc and 5 Vpc regulators

- Internal power on reset

- RoHS compliant

- MSL3

- Emergency power management supporting four configurable power bank I/Os

- Can be cascaded to up to 12 PoE devices (96 ports)

# 2.2 Typical Application

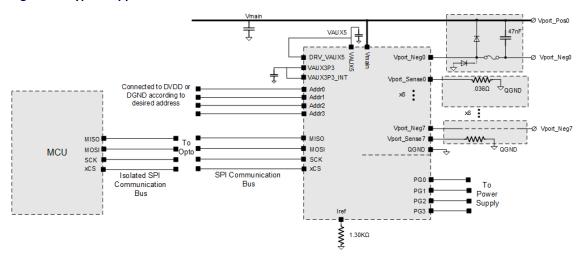

This typical application illustrates a simple PoE system solution for eight Ethernet ports, switch, or hub.

The positive (POS) and negative (NEG) signals should be connected to the switch RJ45 jack.

Figure 1 • Typical Application

**Note**: Fuses per port are not required for use in circuits with total power level of up to 3 kW. The PD69108/F is designed to fulfill limited power source (LPS) requirements per the latest editions of IEC60950-1 and EN60950-1.

For more information on detailed schematics of application and layout recommendations, contact your local Microsemi account representative.

# **3** Functional Descriptions

The PD69108/F has two major sections: a digital section that controls and monitors the logical PoE functions (like state machines and timings) and an analog section that performs the front-end analog PoE functionality.

The following illustration shows the internal functional blocks of the PD69108/F device.

ADDR[3:0] PG[3:0] **♦** Vmain Digital Analog Voltage Regulator (Miscellaneous POR sync Power bank General counter Analog IC ctrl) Mesurmen CLK Voltage Generator for CRG AIR Line Detection cs n SPI Control. (CPU/Control (Analog & Classification . Registers) Interface) Thermal Current Limite Controlled Reference VCM (Voltage Current Measurement) Main MOSFE **DGND** AGND Sense Resisto

Figure 2 • PD69108/F Internal Block Diagram

# 3.1 Logic Main Control Module

The logic main control module block includes the digital timing mechanisms and state machines. This synchronizes and activates the PoE functions according to the following MCU control commands:

- Real-time protection (RTP)

- Start-up macro (DVDT)

- Load signature detection (RES DET)

- Classification macro (CLASS)

- Voltage and current monitoring registers (VMC)

- ADC interfacing

- Direct digital signals with analog block

#### 3.1.1 Line Detection Generator

Upon request from the MCU to the main control module, four different voltage levels are generated by the line detection generator. This ensures robust AF/AT line detection functionality.

#### 3.1.2 Classification Generator

Upon request from the MCU to the main control module, the state machine applies a regulated class event and mark event voltage to the ports. This is required by the IEEE standard.

#### 3.1.3 Current Limiter

This circuit continuously monitors the current of powered ports and limits the current to a specific value, according to pre-defined limits as set by AF/AT and current\_set pins. In cases where the current exceeds this specific level, the system starts to measure the elapsed time. If this time period is greater than a preset threshold, the port is disconnected.

#### 3.1.4 Main MOSFET

This is the main power switching FET, used to control PoE current into the load.

#### 3.1.5 Analog-to-Digital Converter (ADC)

A 10-bit analog-to-digital converter, used to convert analog signals into digital registers for the logic control module.

#### 3.1.6 Power on Reset (POR)

This circuit monitors the internal 3.3 V voltage DC levels. If this voltage drops below specific thresholds, a reset signal is generated and the PD69108/F is reset.

# 3.1.7 Voltage Regulator

The voltage regulator generates  $3.3 \text{ V}_{DC}$  and  $5 \text{ V}_{DC}$  for the internal circuitry. These voltages are derived from the V MAIN supply. To use the internal voltage regulator connect:

- VAUX5 to DRV VAUX5

- VAUX3P3 to VAUX3P3 INT

- REG EN N to AGND

There are two options to reduce the PD69108/F power dissipation by regulating the voltage outside the chip:

- Use an external NPN transistor to regulate the 5 V<sub>DC</sub>. In this setup, the configuration of the regulator's pins should be:

- DRV VAUX5 is connected to the NPN BASE

- VAUX5 is connected to the NPN EMITTER

(Connect the Collector to VMAIN)

- VAUX3P3 is connected to VAUX3P3\_INT

- REG\_EN\_N is connected to AGND

- Supply the PD69108/F with an external 3.3 V voltage regulator. In this setup, the configuration of the regulators pins should be:

- VAUX5 is connected to DRV\_VAUX5

- VAUX3P3 INT is connected to VAUX5

- VAUX3P3 is connected to the external 3.3 V

- REG\_EN\_N is connected to VAUX3P3

The above two options can be implemented simultaneously.

#### 3.1.8 CLK

CLK is an internal 8 MHz clock oscillator.

# 3.2 Application Information

The PD69108/F performs IEEE 802.3af and IEEE 802.3at functionality as well as legacy (capacitor) and Cisco PD detection, in addition to protections such as short circuit and dV/dT protection upon startup.

#### 3.2.1 Line Detection

The line detection feature detects a valid AF or AT load, as specified in the AF/AT standard. The resistor value should range from 19K  $\Omega$  to 26.5K  $\Omega$ . Line detection is based on four different voltage levels generated over the PD (the load), as shown in the following illustration.

Power "ON"

2 Events

Classification Phase

Start-Up

(Inrush)

Detection

Phase

Figure 3 • Typical PoE Voltage Timing Diagram

# 3.2.2 Legacy (Capacitor) Detection

In cases where legacy is set, the PD69108/F's detection mechanism is configured to detect and power-up legacy PDs, as well as AF/AT-compliant. This mechanism also detects and powers up Cisco legacy PDs.

#### 3.2.3 Classification

The classification process takes place right after the resistor detection, when the resistor detection has completed successfully. The main goal of the classification process is to detect the PD class, as specified in the IEEE 802.3AF and AT standards. In AF mode, the classification mechanism is based on a single voltage level (single finger). In AT mode, the classification mechanism is based on two voltage levels (dual finger), as defined in IEEE 802.3at-2009.

# 3.2.4 Port Start Up

Upon a successful detection and classification process, power is applied to the load through a controlled start-up mechanism. During this period, current is limited to 425 mA for a typical duration of 65 mS, which enables the PD load to charge and to enter a steady state power condition.

#### 3.2.5 Over-Load Detection and Port Shut Down

After power up, the PD69108/F automatically initializes its internal protection mechanisms to monitor and disconnect power from the load in cases where extreme conditions (such as over-current or short port terminal scenarios) occur, as specified in the IEEE 802.3AF/AT standard.

#### 3.2.6 Disconnect Detection

The PD69108/F supports the DC disconnect function as per the IEEE 802.3AF/AT standard. This mechanism continuously monitors the load current and disconnects power in cases where the load current is below 7.5 mA (typical) for more than 322 mS.

# 3.2.7 Over-Temperature Protection

The PD69108/F has internal temperature sensors that continuously monitor the main MOSFET junction temperature and disconnect load power when the junction temperature exceeds 200 °C. This mechanism protects the device from extreme events such as high ambient temperature or other thermo-mechanical failures that may damage the PD69108/F.

# 3.2.8 V MAIN Out-of-Range Protection

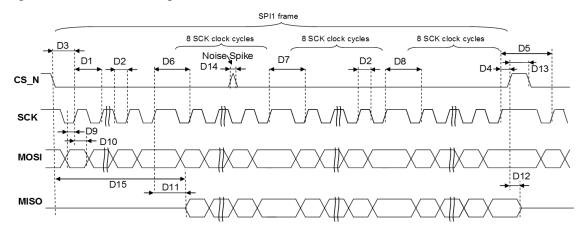

The PD69108/F automatically disconnects port power when  $V_{MAIN}$  exceeds 60  $V_{DC}$ . This is an extremely valuable feature that protects the load if the main power source is faulty or damaged. The following image shows the SPI detailed timing information.

Figure 4 • SPI Detailed Timing Information

The following table describes the SPI timing details.

**Table 1 • SPI Timing Details**

| Name | Min Delay                     | Max Delay                      | Description                                                                  |

|------|-------------------------------|--------------------------------|------------------------------------------------------------------------------|

| D1   | 714 ns                        |                                | SPI clock period                                                             |

| D2   | 45 ns                         | 55 ns                          | SPI duty cycle                                                               |

| D3   | 340 ns                        |                                | SPI_CS setup to SPI clock Positive Edge (delay after SPI_CS active signal)   |

| D4   | 340 ns                        |                                | SPI_CS hold to SPI clock Positive Edge (delay before SPI_CS inactive signal) |

| D5   | 2 SPI clock cycles            |                                | Delay between last SCK in eSPI1 frame and first SCK at adjacent eSPI1 frame. |

| D6   | 1 SPI clock cycles            |                                | Between byte 0 (IC addr) and byte 1(addr).                                   |

| D7   | 1 SPI clock cycles            |                                | Between byte 1 (addr) and byte 2(data).                                      |

| D8   | 1 SPI clock cycles            |                                | Between byte 2 (MS data byte) and byte 3(LS data byte).                      |

| D9   | 340 ns                        |                                | MOSI setup time                                                              |

| D10  | 210 ns                        |                                | MOSI hold time                                                               |

| D11  | 140 ns                        |                                | MISO tri-state to valid data from clock positive edge.                       |

| D12  |                               | 300 ns                         | MISO valid data to tri-state from SPI_CS positive edge.                      |

| D13  | 1 SPI clock cycles            |                                | SPI_CS width (Delay eSPI1 frame to adjacent eSPI1 frame).                    |

| D14  |                               | 60 ns                          | Filtered Glitch Width                                                        |

| D15  | D3 + 15.5 SPI clock<br>cycles | D3 + 23.75 SPI clock<br>cycles | MISO tri-state from SPI_CS negative edge to valid data.                      |

# **4** Electrical Specifications

The following specifications apply to the operating ambient temperature.

Table 2 • PD69108/F Power Supply

| Parameter                              | Symbol              | Test Conditions/<br>Comment                   | Min. | Тур. | Max. | Unit            |

|----------------------------------------|---------------------|-----------------------------------------------|------|------|------|-----------------|

| Input voltage                          | V <sub>MAIN</sub>   | Supports full IEEE 802.3 functionality        | 44   | 55   | 57   | V               |

| Power supply current at operating mode |                     | V <sub>MAIN</sub> = 55 V <sub>DC</sub>        |      |      | 20   | mA              |

| 5 V output voltage                     | V <sub>AUX5</sub>   |                                               | 4.5  | 5    | 5.5  | VDC             |

| 3.3 V output voltage                   | V <sub>AUX3P3</sub> |                                               | 2.97 | 3.3  | 3.63 | VDC             |

| 3.3 V output current                   |                     | Without external NPN                          |      |      | 5    | mA              |

|                                        |                     | With external NPN transistor on Vauxs         |      |      | 30   | mA              |

| 3.3 V input voltage                    | V <sub>AUX3P3</sub> | REG_EN_N pin = 3.3 V                          | 3    | 3.3  | 3.6  | V <sub>DC</sub> |

|                                        |                     | (internal reg. is disabled) VAUX3P3_INT = 5 V |      |      |      |                 |

# Table 3 • Digital I/O

| Parameter                   | Symbol | Test Conditions/<br>Comment | Min. | Тур. | Max. | Unit |

|-----------------------------|--------|-----------------------------|------|------|------|------|

| Input logic, high threshold | ViH    |                             | 2.2  |      |      | V    |

| Input logic, low threshold  | VIL    |                             |      |      | 0.8  | V    |

| Input hysteresis voltage    |        |                             | 0.4  | 0.6  | 8.0  | V    |

| Input high current          | Іін    |                             | -10  |      | 10   | μΑ   |

| Input low current           | liL    |                             | -10  |      | 10   | μΑ   |

| Output high voltage         | Vон    | For IoH = -1 mA             | 2.4  |      |      | V    |

| Output low voltage          | Vol    | Iон = 1 mA                  |      |      | 0.4  | V    |

# **Table 4 • PoE Load Currents**

| Parameter        | Symbol                        | Test Conditions/Comment        | Min. | Тур. | Max. | Unit |

|------------------|-------------------------------|--------------------------------|------|------|------|------|

| AF, limit mode   | AF_LIM                        |                                | 400  | 425  | 450  | mA   |

| AT limit         | AT_LIM                        |                                | 775  | 850  | 925  | mA   |

| AT limit dynamic | Configurable by communication | R <sub>SENSE</sub> = 0.36 Ω 1% | 540  |      | 1200 | mA   |

| range            | communication                 | connected at Port_Sense pin    |      |      |      |      |

**Table 5 • Main Power Switching FET**

| Parameter                             | Symbol  | Тур. | Unit |

|---------------------------------------|---------|------|------|

| On resistance                         | Rds(on) | 0.3  | Ω    |

| Internal thermal protection threshold |         | 200  | °C   |

# 4.1 Dynamic Characteristics

The PD69108/F utilizes three current level thresholds (IMIN, ICUT, ILIM) and three timers (TMIN, TCUT, TLIM).

- Loads that consume ILIM current for more than TLIM are labeled as "short circuit state" and shut down.

- Loads that dissipate more than I<sub>CUT</sub> for longer than T<sub>CUT</sub> are labeled as overloads and are automatically shut down.

- If output power is below Imin for more than Tmin, the PD is labeled as "no load" and is shut down.

Automatic recovery from overload and no load conditions is attempted every Tovlrec periods (typically, 1 second). Output power is limited to ILIM, which is a maximum peak current allowed at the port.

Table 6 • IEEE 802.3 AF Mode Parameters

| Parameter                                                 | Symbol            | Conditions                                                                                                             | Min. | Тур. | Max. | Unit |

|-----------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Automatic<br>recovery from no<br>load shutdown            |                   | Tudlrec value, measured from port shutdown point (can be modified through control port)                                |      | 1    |      | S    |

| Cutoff timer                                              |                   | Typical accuracy of                                                                                                    |      | 2    |      | ms   |

| accuracy                                                  |                   | Tcut                                                                                                                   |      |      |      |      |

| Inrush current                                            | linrsh            | For t = 50 ms,<br>$C_{load} = 180 \mu F (max)$                                                                         | 400  |      | 450  | mA   |

| Output current operating range                            | IPORT             | Continuous operation after startup period                                                                              | 10   |      | 350  | mA   |

| Output power<br>available<br>operating range              | Ррокт             | Continuous operation after startup period, at port output                                                              | 0.57 |      | 15.4 | W    |

| Off-mode current                                          | I <sub>MIN1</sub> | Must disconnect for T greater than TuvL                                                                                | 0    |      | 5    | mA   |

|                                                           | I <sub>MIN2</sub> | May or may not disconnect when T is greater than $\ensuremath{T_{\text{UVL}}}$                                         | 5    | 7.5  | 10   | mA   |

| PD power<br>maintenance<br>request drop-out<br>time limit | Трмдо             | Buffer period to handle transitions                                                                                    | 300  |      | 400  | ms   |

| Over-load current detection range                         | Ісит              | Time limited to TovL                                                                                                   | 350  |      | 400  | mA   |

| Over-load time                                            | TovL              |                                                                                                                        | 50   |      | 75   | ms   |

| Turn-on rise time                                         | Trise             | From 10% to 90% of $V_{port}$ (specified for PD load consisting of 100 $\mu F$ capacitor in parallel to 200 $\Omega$ ) | 15   |      |      | μs   |

| Turn-off time                                             | Toff              | From Vport to 2.8 Vpc                                                                                                  |      |      | 500  | ms   |

| Parameter                     | Symbol | Conditions                           | Min. | Тур. | Max. | Unit |

|-------------------------------|--------|--------------------------------------|------|------|------|------|

| Time maintain power signature | Тмрѕ   | DC modulation time for DC disconnect |      | 49   |      | ms   |

# Table 7 • IEEE 802.3 AT Mode Parameters

| Parameter                                        | Symbol            | Conditions                                                                                                              | Min. | Тур. | Max. | Unit |

|--------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Automatic recovery from no load shutdown         |                   | Tudlrec value, measured from port shutdown point (can be modified through control port)                                 |      | 1    |      | Sec  |

| Cutoff timer accuracy                            |                   | Typical accuracy of T <sub>cut</sub>                                                                                    |      | 2    |      | ms   |

| Inrush current                                   | Inrsh             | For t = 50 ms, $C_{load}$ = 180 $\mu$ F (max)                                                                           | 400  |      | 450  | mA   |

| Output current operating range                   | <b>I</b> PORT     | Continuous operation after startup period                                                                               | 10   |      | 600  | mA   |

| Output power available operating range           | PPORT             | Continuous operation after startup period, at port output                                                               | 0.57 |      | 36   | W    |

| Off-mode current                                 | I <sub>MIN1</sub> | Must disconnect when T is greater than Tuvl                                                                             | 0    |      | 5    | mA   |

|                                                  | I <sub>MIN2</sub> | May or may not disconnect when T is greater than Tuv.                                                                   | 5    | 7.5  | 10   | mA   |

| PD power maintenance request drop-out time limit | Трмдо             | Buffer period to handle transitions                                                                                     | 300  |      | 400  | ms   |

| Over-load current detection range                | Ісит              | Time limited to TovL                                                                                                    | 600  |      | 775  | mA   |

| Over-load time limit                             | Tovl              |                                                                                                                         | 50   |      | 75   | ms   |

| Turn-on rise time                                | Trise             | From 10% to 90% of $V_{port}$ (specified for PD load consisting of 100 $\mu$ F capacitor in parallel to 200 $\Omega$ ). | 15   |      |      | μs   |

| Turn-off time                                    | Toff              | From V <sub>port</sub> to 2.8 V <sub>DC</sub>                                                                           |      |      | 500  | ms   |

| Time maintain power signature                    | Тмрѕ              | DC modulation time for DC disconnect                                                                                    |      | 49   |      | ms   |

# 4.2 Absolute Maximum Ratings

The following table shows the absolute maximum ratings for the PD69108.

Exceeding these ratings can cause damage to the device. All voltages are with respect to ground. Currents are marked positive when flowing into a specified terminal and marked negative when flowing out of a specified terminal.

**Table 8 • Absolute Maximum Ratings**

| Parameter                                    | Rating                                      |

|----------------------------------------------|---------------------------------------------|

| Supply input voltage (V <sub>MAIN</sub> )    | -0.3 Vpc to 74 Vpc                          |

| Port_Neg [07] pins                           | -0.3 Vpc to 74 Vpc                          |

| Port_Sense [07] pins                         | -0.3 Vpc to 3.6 Vpc                         |

| QGND, GND pins                               | -0.3 V <sub>DC</sub> to 0.3 V <sub>DC</sub> |

| All other pins                               | -0.3 V <sub>DC</sub> to 3.6 V <sub>DC</sub> |

| PD69108 Operating ambient temperature range  | −10 °C to 85 °C                             |

| PD69108F Operating ambient temperature range | –40 °C to 85 °C                             |

| Maximum operating junction temperature       | 150 °C                                      |

| Storage temperature range                    | −65 °C to 150 °C                            |

| ESD protection at all I/O pins               | JESD22 Class 1C HBM (±2KV)                  |

# 4.3 Power Dissipation Information

The following table shows the power dissipation values of the respective parameters.

**Table 9 • Power Dissipation**

| Parameter                                                           | Value                                 |

|---------------------------------------------------------------------|---------------------------------------|

| Rsense power dissipation                                            | $0.36 \Omega \times I_{PORT}^2$       |

| Rds_ON power dissipation                                            | $0.3 \Omega \times I_{PORT^2}$        |

| Pport_AF = 15.4 W                                                   | PRsense = 28.2 mW                     |

|                                                                     | PRds_ON = 23.4 mW                     |

| Pport_AT = 30 W                                                     | PRsense = 107 mW                      |

| NOTE: Calculated for supply input voltage of 55 V.                  | PRds_ON = 88.5 mW                     |

| PD69108 self power dissipation (including internal 3.3 V regulator) | 1.1 W                                 |

| PD69108 8 ports AF application power dissipation                    | 1.1 W + [ 8 × (28.2 mW + 23.4 mW) ] = |

|                                                                     | 1.51 W                                |

| PD69108 8 ports AT application power dissipation                    | 1.1 W + [ 8 × (107 mW + 88.5 mW) ] =  |

|                                                                     | 2.66 W                                |

| PD69108 self power dissipation (including external 3.3 V regulator) | 0.5 W                                 |

| PD69108 AF 8 ports application power dissipation                    | 0.5 W + [ 8 × (28.2 mW + 23.4 mW) ] = |

|                                                                     | 0.91 W                                |

| PD69108 8 ports AT application power dissipation                    | 0.5 W + [ 8 × (107 mW + 88.5 mW) ] =  |

|                                                                     | 2.06 W                                |

# **5** Pin Descriptions

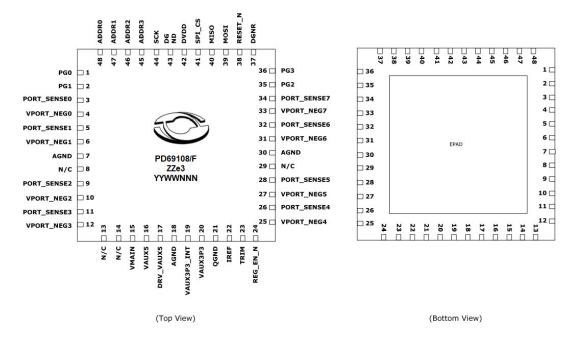

The following illustration shows the pin diagram (top and bottom views) for the PD69108/F device.

Figure 5 • PD69108/F Pinout

- PD69108 for –10 °C to 85 °C operating ambient temperature range

- PD69108F for –40 °C to 85 °C operating ambient temperature range

The following table shows the pin descriptions for the PD69108/F device.

**Table 10 • Pin Descriptions**

| Number | Name        | Туре       | Description                                                                     |

|--------|-------------|------------|---------------------------------------------------------------------------------|

|        | EPAD        | Analog     | Exposed pad; metal plate on the IC bottom side connected to analog ground.      |

|        |             | ground     | A high-quality ground plane (about 500 mil. inch over 500 mil. inch) should be  |

|        |             |            | deployed around this pin whenever possible.                                     |

| 1      | PG0         | Digital    | Power supply monitoring                                                         |

| 2      | PG1         | input      |                                                                                 |

| 3      | PORT_SENSE0 | Analog     | Sense resistor port input                                                       |

|        |             | input      | (Connected to 0.36 $\Omega,$ 1% resistor to QGND with ~12 $m\Omega$ trace for   |

|        |             |            | measurements accuracy).                                                         |

| 4      | VPORT_NEG0  | Analog I/O | Negative port output                                                            |

| 5      | PORT_SENSE1 | Analog     | Sense resistor port input                                                       |

|        |             | input      |                                                                                 |

|        |             |            | (Connected to 0.36 $\Omega$ , 1% resistor to QGND with ~12 m $\Omega$ trace for |

|        |             |            | measurements accuracy).                                                         |

| 6      | VPORT_NEG1  | Analog I/O | Negative port output                                                            |

| 7      | AGND        | Power      | Analog ground.                                                                  |

| Number | Name        | Туре            | Description                                                                                                                                                                                                                                                                       |

|--------|-------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8      | N/C         | Power           | Not Connected                                                                                                                                                                                                                                                                     |

| 9      | PORT_SENSE2 | Analog<br>input | Sense resistor port input (Connected to 0.36 $\Omega$ , 1% resistor to QGND with ~12 m $\Omega$ trace for measurements accuracy)                                                                                                                                                  |

| 10     | VPORT_NEG2  | Analog I/O      | Negative port output                                                                                                                                                                                                                                                              |

| 11     | PORT_SENSE3 | Analog<br>input | Sense resistor port input (Connected to 0.36 $\Omega$ , 1% resistor to QGND with ~12 m $\Omega$ trace for measurements accuracy)                                                                                                                                                  |

| 12     | VPORT_NEG3  | Analog<br>I/O   | Negative port output                                                                                                                                                                                                                                                              |

| 13     | N/C         | Analog I/O      | Test pin (for production use only); keep open (not connected).                                                                                                                                                                                                                    |

| 14     | N/C         | _               |                                                                                                                                                                                                                                                                                   |

| 15     | VMAIN       | Power           | Supplies voltage for the internal analog circuitry. A low ESR 1 $\mu$ F (or higher) bypass capacitor, connected to AGND should be placed as close as possible to this pin through low resistance traces.                                                                          |

| 16     | VAUX5       | Power           | Regulated 5 V <sub>DC</sub> output voltage source; it needs to be connected to a filtering capacitor of 4.7 $\mu$ F or higher. If an external NPN is used to regulate the voltage, connect this pin to the "Emitter" (the "collector" should be connected to V <sub>MAIN</sub> ). |

| 17     | DRV_VAUX5   | Power           | Zapping input for IC production trimming. Should be connected to DVDD.                                                                                                                                                                                                            |

| 18     | AGND        | Power           | Analog ground                                                                                                                                                                                                                                                                     |

| 19     | VAUX3P3_INT | Power           | Connected to VAX3P3 (pin 20) if internal 3.3 V <sub>DC</sub> regulator is used.  Connect to VAUX5 (pin 16) if external 3.3 V <sub>DC</sub> regulator is used.                                                                                                                     |

| 20     | RESET_N     | Power           | Regulated 3.3 V output voltage source. A 4.7 $\mu$ F or higher filtering capacitor should be connected between this pin and AGND. When an external 3.3 Vocregulator is used, connect it to this pin to supply the chip.                                                           |

| 21     | QGND        | Power           | Quiet analog ground.                                                                                                                                                                                                                                                              |

| 22     | IREF        | Analog<br>input | Reference resistor pin. Connect a 30.1 k $\Omega$ 1% resistor to QGND.                                                                                                                                                                                                            |

| 23     | TRIM        | Analog<br>input | Trimming Input for IC production. It should be connected to VAUX3P3.                                                                                                                                                                                                              |

| 24     | REG_EN_N    | REG_EN_N        | Enable/Disable the internal 3.3 Voc regulator in case an external 3.3 Voc is used to supply the chip.  GND: Internal regulator enabled.  3.3 VDC: Internal regulator disabled                                                                                                     |

| 25     | Reserved    | Analog I/O      | Keep this pin open (un-connected).                                                                                                                                                                                                                                                |

| 26     | AGND        | Allulog I/O     | Connect to analog ground                                                                                                                                                                                                                                                          |

| 27     | Reserved    |                 | Keep this pin open (un-connected)                                                                                                                                                                                                                                                 |

| 28     | AGND        |                 | Connect to analog ground                                                                                                                                                                                                                                                          |

| 29     | N/C         |                 | Not Connected                                                                                                                                                                                                                                                                     |

| 30     | AGND        | Power           | Analog ground                                                                                                                                                                                                                                                                     |

| 31     | Reserved    |                 | Keep this pin open (un-connected)                                                                                                                                                                                                                                                 |

| J1     | ACSCI VEU   |                 | Reep and pin open (an connected)                                                                                                                                                                                                                                                  |

| Number | Name     | Туре              | Description                                                                                                            |

|--------|----------|-------------------|------------------------------------------------------------------------------------------------------------------------|

| 32     | AGND     |                   | Connect to analog ground                                                                                               |

| 33     | Reserved |                   | Keep this pin open (un-connected)                                                                                      |

| 34     | AGND     |                   | Connect to analog ground                                                                                               |

| 35     | PG2      | Digital           | Power supply monitoring                                                                                                |

| 36     | PG3      | input             |                                                                                                                        |

| 37     | TST      | Digital I/O       | Test pin for production use only. Keep connected to DGND.                                                              |

| 38     | RESET_N  | Digital<br>input  | Reset input; active low ('0' = reset)  An external 10K pull-up resistor should be connected between this pin and DVDD. |

| 39     | MOSI     | Digital<br>input  | SPI bus, Master Data out/slave in                                                                                      |

| 40     | MISO     | Digital<br>output | SPI bus, Master Data in/slave out                                                                                      |

| 41     | SPI_CS   | Digital<br>input  | SPI bus, Chip Select                                                                                                   |

| 42     | DVDD     | Power             | Digital 3.3 V input. It needs to be connected to filtering capacitor of 1 $\mu\text{F}.$                               |

| 43     | DGND     | Digital I/O       | Digital GND                                                                                                            |

| 44     | SCK      | Digital<br>input  | SPI bus, serial clock input                                                                                            |

| 45     | ADDR3    | Digital<br>input  | SPI address bit 3 to set chip address.                                                                                 |

| 46     | ADDR2    | Digital<br>Input  | SPI address bit 2 to set chip address.                                                                                 |

| 47     | ADDR1    | Digital<br>input  | SPI address bit 1 to set chip address.                                                                                 |

| 48     | ADDR0    | Digital<br>input  | SPI address bit 0 to set chip address.                                                                                 |

Address Pin Description (ADDR<3:0>)

The following tables shows the address pin description for the PD69108/F device.

Note: 0 = Connect to DGND (digital ground), 1 = connect to DVDD (3.3 V).

Table 11 • Address Pin Description

| ADDR3 | ADDR2 | ADDR1 | ADDR0 | SPI ADDRESS [HEX] |

|-------|-------|-------|-------|-------------------|

| 0     | 0     | 0     | 0     | 0                 |

| 0     | 0     | 0     | 1     | 1                 |

| 0     | 0     | 1     | 0     | 2                 |

| 0     | 0     | 1     | 1     | 3                 |

| 0     | 1     | 0     | 0     | 4                 |

| 0     | 1     | 0     | 1     | 5                 |

| ADDR3 | ADDR2 | ADDR1 | ADDR0 | SPI ADDRESS [HEX] |

|-------|-------|-------|-------|-------------------|

| 0     | 1     | 1     | 0     | 6                 |

| 0     | 1     | 1     | 1     | 7                 |

| 1     | 0     | 0     | 0     | 8                 |

| 1     | 0     | 0     | 1     | 9                 |

| 1     | 0     | 1     | 0     | A                 |

| 1     | 0     | 1     | 1     | В                 |

| 1     | 1     | 0     | 0     | С                 |

| 1     | 1     | 0     | 1     | D                 |

| 1     | 1     | 1     | 0     | E - Broadcast 1   |

| 1     | 1     | 1     | 1     | F                 |

# Note:

1. This address is used for Broadcast. Do not set any PD69108/Fs in the system to this address.

# **6** Package Specification

This section shows the package drawing, RoHS and solder reflow information, and thermal specifications for the PD69108/F device.

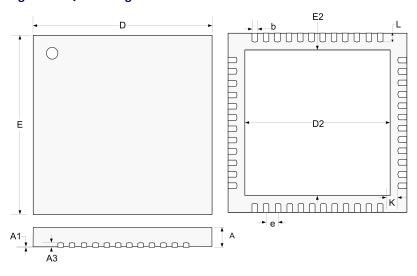

The following illustration shows the QFN package for the PD69108/F device. This package measures 8 mm by 8 mm and is a 48-pin QFN.

Figure 6 • QFN Package

The dimensions do not include protrusions. The protrusions do not exceed 0.155 mm (0.006 in) on any side. The lead dimensions do not include solder coverage.

The following table shows the dimensions for the QFN package.

**Table 12 • Package Dimensions**

| Dimension | Millimeters |      | Inches    |       |

|-----------|-------------|------|-----------|-------|

|           | Min.        | Max. | Min.      | Max.  |

| Α         | 0.80        | 1.00 | 0.031     | 0.039 |

| A1        | 0.00        | 0.05 | 0         | 0.002 |

| A3        | 0.20 REF    |      | 0.008 REF |       |

| K         | 0.20 MIN    |      | 0.008 MIN |       |

| е         | 0.50 BSC    |      | 0.02 BSC  |       |

| L         | 0.30        | 0.50 | 0.012     | 0.02  |

| b         | 0.18        | 0.30 | 0.007     | 0.012 |

| D2        | 6.35        | 6.60 | 0.250     | 0.260 |

| E2        | 6.35        | 6.60 | 0.250     | 0.260 |

| D         | 8.00 BSC    |      | 0.315 BSC |       |

| E         | 8.00 BSC    |      | 0.315 BSC |       |

| E         | 8.00 BSC    |      | 0.315 BSC |       |

# 6.1 RoHS and Solder Reflow Information

The PD69108/F device is rated RoHS 6/6. The package is lead(Pb)-free, with a 100% matte tin finish. The package peak temperature for solder reflow (40 seconds maximum exposure) is 260 °C (0 °C–5 °C).

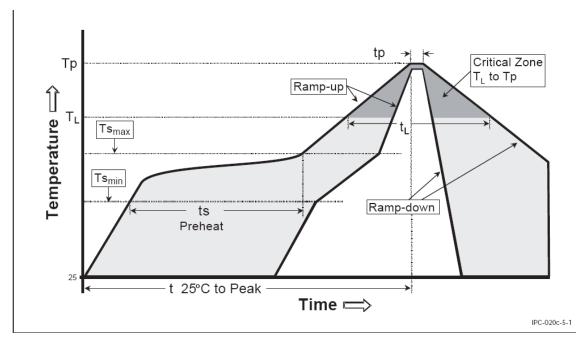

The following table shows the classification reflow profile information.

**Table 13 • Classification Reflow Profiles**

| Profile Feature                                   | Pb-Free Assembly |

|---------------------------------------------------|------------------|

| Average ramp-up rate (TS <sub>max</sub> to Tp)    | 3 °C/s max       |

| Preheat                                           | 150 °C           |

| Temperature min (TS <sub>min</sub> )              | 200 °C           |

| Temperature max (TS <sub>max</sub> )              | 60–180 s         |

| Time (ts <sub>min</sub> to ts <sub>max</sub> )    |                  |

| Time maintained                                   | 217 °C           |

| Temperature (T <sub>L</sub> )                     | 60–150 s         |

| Time (tı)                                         |                  |

| Peak classification temperature (T <sub>P</sub> ) | 240 - 255 °C     |

| Time within 5 °C of actual peak temperature (tp)  | 20–40 s          |

| Ramp-down rate                                    | 6 °C/s max       |

| Time 25 °C to peak temperature                    | 8 minutes max    |

Note: All temperatures refer to topside of the package, measured on the package body surface.

**Note**: Exceeding these ratings can cause damage to the device.

Following is the classification reflow profile diagram.

Figure 7 • Classification Reflow Profile Diagram

# **6.2** Thermal Specifications

The following table shows the thermal specifications for the PD69108/F device.

**Table 14 • Thermal Specifications**

| Parameter                                       | Value   |

|-------------------------------------------------|---------|

| Typical thermal resistance: junction to ambient | 25 °C/W |

| Typical thermal resistance: junction to case    | 4 °C/W  |

The  $\theta_{JA}$  numbers are guidelines for the thermal performance of the device/PC-board system. All specifications assume no ambient airflow.

# 6.3 Tape and Reel Packaging Information

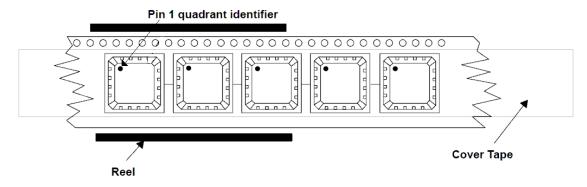

The following figure shows the Pin-1 orientation of QFN packages for the PD69108/F device.

Figure 8 • Pin-1 Orientation of QFN Packages Diagram

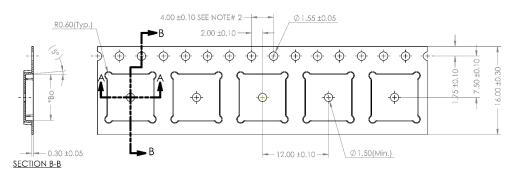

The following figures represents the tape and reel shipment specifications.

**Figure 9 • Tape Shipment Specifications**

The following table shows the tape mechanical data:

Table 15 • Tape Mechanical Data

| Dimensions | (mm)        |

|------------|-------------|

| Ao         | 8.35 ±0.10  |

| Во         | 8.35 ±0.10  |

| Ко         | 1.40 ±0.10  |

| K1         | N/A         |

| Pitch      | 12.00 ±0.10 |

| Width      | 16.00 ±0.30 |

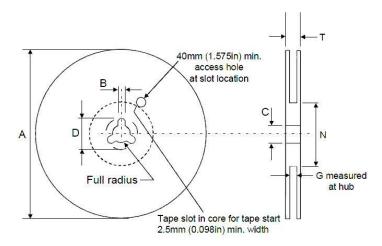

The following image shows the reel shipment specifications for the PD69108/F device.

Figure 10 • Reel Shipment Specifications

The following table lists the reel specification details for the PD69108/F device.

Table 16 • Reel Mechanical Data

| Component     | Dimension (mm) | Dimension (in.)  |

|---------------|----------------|------------------|

| Tape size     | 16.00 ±0.3     | 0.630 ±0.012     |

| A max         | 330            | 13               |

| B max         | 1.5            | 0.059            |

| С             | 13.0 ±0.20     | 0.512 ±0.008     |

| D min         | 20.2           | 0.795            |

| N min         | 50             | 1.968            |

| G             | 16.4+2.0/-0.0  | 0.645+0.079/-0.0 |

| T max         | 29             | 1.142            |

| Base Quantity | 2000 pcs       |                  |

# 7 Ordering Information

# **Table 17 • Ordering Information**

| Part Number | Package                        | Temperature     | Part Marking   |

|-------------|--------------------------------|-----------------|----------------|

| PD69108ILQ  | Plastic 48 pin QFN 8 mm × 8 mm | −10 °C to 85 °C | Microsemi Logo |

|             |                                |                 | PD69108        |

|             |                                |                 | ZZ e3          |

|             |                                |                 | YYWWNNN        |

| PD69108FILQ | Plastic 48 pin QFN 8 mm × 8 mm | −40 °C to 85 °C | Microsemi Logo |

|             |                                |                 | PD69108F       |

|             |                                |                 | ZZ e3          |

|             |                                |                 | YYWWNNN        |

**Note**: Available in tape and reel. Append the letters TR to the part number.

- 1. ZZ e3: ZZ = Random Character with no meaning, and e3 = 2nd Level Interconnect.

- 2. YY = Year, WW = Week, NNN = Trace Code.

#### Microsemi Headquarters

One Enterprise, Aliso Viejo,

CA 92656 USA

Within the USA: +1 (800) 713-4113

Outside the USA: +1 (949) 380-6100

Sales: +1 (949) 380-6136

Fax: +1 (949) 215-4996

Email: sales.support@microsemi.com

© 2015-2019 Microsemi. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products

Microsemi, a wholly owned subsidiary of Microchip Technology Inc. (Nasdaq: MCHP), offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions; security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www microsemi.com.

PD-000307817

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

# Microchip:

PD69108F PD69108 PD69104F PD69104